中华人民共和国国家标准

集成电路封装测试厂设计规范

Codefordesignofintegratedcircuitassemblyandtestfactory

GB51122-2015

主编部门:中华人民共和国工业和信息化部

批准部门:中华人民共和国住房和城乡建设部

施行日期:2016年5月1日

中华人民共和国住房和城乡建设部公告

第887号

住房城乡建设部关于发布国家标准《集成电路封装测试厂设计规范》的公告

现批准《集成电路封装测试厂设计规范》为国家标准,编号为GB51122-2015,自2016年5月1日起实施。其中,第5.3.1条为强制性条文,必须严格执行。

本规范由我部标准定额研究所组织中国计划出版社出版发行。

中华人民共和国住房和城乡建设部

2015年8月27日

前言

本规范是根据住房城乡建设部《关于印发<2012年工程建设标准规范制订、修订计划>的通知》(建标[2012]5号)的要求,由工业和信息化部电子工业标准化研究院电子工程标准定额站和信息产业电子第十一研究院科技工程股份有限公司会同有关单位共同编制完成。

本规范编制过程中,编制组经过广泛调查研究,认真总结实践经验并参考国内外有关标准,广泛吸取了国内有关单位和专家的意见,并反复修改,经审杏定稿。

本规范共分10章和1个附录。主要内容有:总则、术语、工艺设计、厂址选择及布局、建筑与结构、给排水与消防、电气、净化空调及工艺排风、纯水与废水处理、气体与真空等。

本规范中以黑体字标志的条文为强制性条文,必须严格执行。

本规范由住房城乡建设部负责管理和对强制性条文的解释,工业和信息化部负责日常管理,信息产业电子第十一设计研究院科技工程股份有限公司负责具体技术内容的解释。执行过程中如有意见或建议请寄至信息产业电子第十一设计研究院科技工程股份有限公司《集成电路封装测试厂设计规范》管理组(地址:四川省成都市双林路251号,邮政编码:610021,传真:028-84333172)。

本规范主编单位、参编单位、主要起草人和主要审查人:

主编单位:工业和信息化部电子工业标准化研究院电子工程标准定额站

信息产业电子第十一设计研究院科技工程股份有限公司

参编单位:中国电子工程设计院

江苏长电科技股份有限公司

无锡华润微电子有限公司

主要起草人:王毅勃江元升李骥肖劲戈黄华敬王春夏双兵车俊朱琳周向荣肖红梅黄一义宋祝宁王明云闫诗源

主要审查人:陈霖新王开源郑秉孝张人茂童大江陈光鸿李建强薛长立何为

以下规范内容由合景净化工程公司www.hejiejh.com进行整理编辑

2术语

2.0.1晶圆wafer

经过集成电路前工序加工后,形成了电路管芯的硅或其他化合物半导体的圆形单晶片。

2.0.2中测chiptesting

对完成前工序工艺的晶圆进行器件标准和功能性电学测试。

2.0.3磨片wafergrinding

通过磨轮磨削等手段对晶圆背面减薄,以满足划片加工的厚度要求。

2.0.4划片wafersaw

将减薄后的晶圆切割成独立的芯片。

2.0.5粘片diebond

将切割好的芯片置放到引线框架或封装衬底或基座条带上。

2.0.6焊线wirebond

芯片上的引线孔通过金线或铜线等与框架衬底上的引脚连接,使芯片电路能与外部电路连通。

2.0.7塑封molding

环氧树脂经模注、灌封、压入等工序将芯片、框架或基板、电极引线等封为一体。

2.0.8电镀plating

在框架引脚上形成保护性镀层,以增强可焊性。

2.0.9成品测试testing

对包封后的集成电路产品分选测试的过程。

2.0.10晶圆级封装waferlevelpackaging

在完整晶圆上完成包括成品测试在内的各道工艺,最后切割成单个电路的封装形式。

2.0.11通孔throughsiliconvia

采用深层等离子刻蚀、激光加工或湿法刻蚀等方式在芯片和芯片之间、晶圆和晶圆之间制作垂直导通。

2.0.12凸块bumping

采用金、铅锡或铜等材料利用薄膜或化学镀工艺制成倒装芯片电路的接触点。

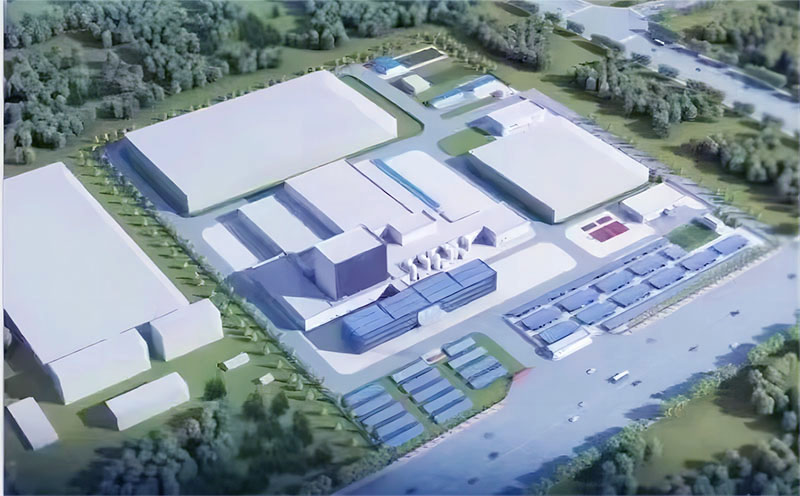

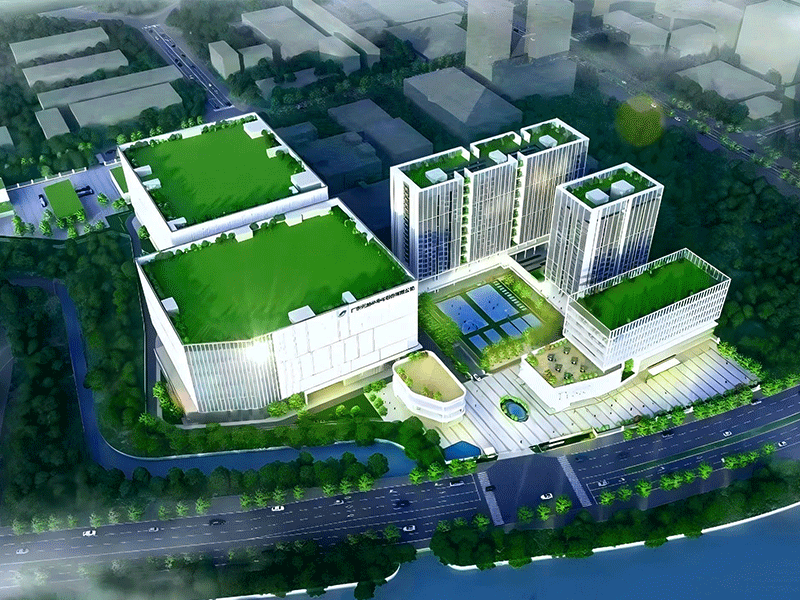

图为合景净化工程公司洁净厂房完工案例

3工艺设计

3.1一般规定

3.1.1生产环境宜符合表3.1.1的要求。

表3.1.1生产环境需求表

3.1.2生产过程所使用纯水的电阻率应符合下列规定:

1用于硅片清洗的纯水电阻率不宜低于15MΩ·cm;

2用于硅片划片的纯水电阻率宜在0.5MΩ·cm~1MΩ·cm范围内;

3用于电镀工艺的纯水电阻率不宜低于2MΩ·cm。

3.1.3生产过程所使用气体的品质应符合下列规定:

1用于通孔、凸块工序的气体纯度不宜低于99.9999%、露点不宜低于—60℃;

2用于中测、磨片、划片、粘片、焊线、塑封等工序的气体纯度宜在99.99%~99.9999%范围内、露点宜在—40℃~—60℃范围内。

3.2技术设备

3.2.1工艺技术应根据芯片互联及封装的类型确定,并应具有扩展的灵活性。

3.2.2工艺设计应明确技术设备的各种工艺条件,做到投资省、运行费用低。

3.2.3生产设备的选择应符合下列规定:

1设备选择应根据产品类型及产能要求确定各工序设备数量;

2生产设备自动化程度应适应产能的要求;

3生产设备应适应连续运行的要求。

3.3工艺布局

3.3.1工艺布局应符合下列规定:

1生产设备应按照工艺流程顺序布置,避免交叉;

2辅助设施应靠近生产区;

3物流人流应分开设置。

3.3.2生产区应设置单独的设备和物料出入口,并应配置相应的物料净化设施。

3.3.3生产区净高应根据生产设备及安装确定。

3.3.4生产区内宜设置原材料、成品及设备备品备件暂存区域。

3.3.5生产区应设置单独人员出入口,人员进入7级以上净化区应经过风淋系统。

3.3.6生产区操作人员走道宽度应根据设备操作、人员通行及材料搬运需要确定。

3.3.7生产洁净区宜设置参观走道。

4厂址选择及布局

4.1厂址选择

4.1.1厂址选择应符合国家及地方总体规划要求,宜选择在远离散发大量粉尘、有严重空气污染的区域。

4.1.2厂址选择应考虑市政给排水、动力供应、通信设施完善和交通便利等因素。

4.2总平面布局

4.2.1厂区总平面布局应适应生产工艺特点及技术升级。

4.2.2厂区应根据产品生产要求确定,宜按办公、生产、仓储、动力功能进行布局。

4.2.3厂区人流、物流出入口宜分开设置。

4.2.4厂区车辆停放场地应根据物流、人员数量及当地交通状况构成特点确定。

4.2.5生产厂房宜设环形消防通道或沿厂房长边的两侧设消防通道。

4.2.6厂区道路路面应采用整体性能好、发尘少的材料。

4.2.7厂区内绿化宜采用无飞絮的常绿树种和草皮。

5建筑与结构

5.1建筑

5.1.1生产厂房的建筑平面和空间布局应满足产品工艺要求,并应适应工厂发展及技术升级。

5.1.2生产厂房外围构造应满足生产工艺对气密、保温、隔热、防潮、易清洗的要求。

5.1.3生产厂房应设置设备运输安装通道,并宜设置货梯、吊装口及吊装平台。

5.1.4生产厂房外窗宜采用节能型窗。

5.1.5生产厂房电镀区地面应进行防腐处理。

5.1.6装修和密封材料应符合现行国家标准《电子工业洁净厂房设计规范》GB50472和《建筑内部装修设计防火规范》GB50222的有关规定。

5.1.7装修材料的烟密度等级应符合现行国家标准《建筑材料燃烧或分解的烟密度试验方法》GB/T8627的有关规定。

5.2结构

5.2.1生产厂房应根据抗震设防类别及地震烈度等级进行抗震设计,并应符合现行国家标准《建筑工程抗震设防分类标准》GB50223的有关规定。

5.2.2生产厂房的主体结构应满足生产工艺要求,宜采用大跨度钢筋混凝土框架结构、钢结构或两种结构的组合。

5.2.3生产厂房柱网尺寸宜采用600mm的模数。

5.2.4生产厂房变形缝不宜穿越洁净生产区。

5.2.5生产厂房为无缝超长混凝土结构时,应采取防开裂设计措施。

5.2.6生产厂房当有微振控制要求时,应采取相应防微振措施。

5.3防火与疏散

5.3.1生产厂房的耐火等级不应低于二级。

5.3.2生产厂房的火灾危险性分类应为丙类,防火分区的划分应满足工艺生产的要求,并应符合现行国家标准《电子工业洁净厂房设计规范》GB50472的有关规定。

5.3.3每一生产层、每个防火分区或每一洁净区的安全出口设计应符合下列规定:

1安全出口数量应符合现行国家标准《洁净厂房设计规范》GB50073的有关规定;

2安全出口应分散布置,并应设有明显的疏散标志;

3安全疏散距离可根据生产工艺确定,应符合现行国家标准《电子工业洁净厂房设计规范》GB50472的有关规定。

6给排水与消防

6.1给排水

6.1.1给排水系统应满足生产、生活、消防以及环保等要求,并应根据水质、水压、水温的要求分别设置。

6.1.2生产和生活给水系统宜利用市政给水管网的水压直接供水。

6.1.3当市政给水管网水压、水量不能满足要求时,生产、生活给水系统应设置贮水装置和加压装置。并应符合下列规定:

1贮水装置不得影响水质;

2加压装置宜采用变频调速设备;

3加压装置应设置备用泵,备用泵供水能力不应小于供水泵中最大一台的供水能力。

6.1.4洁净区内工艺设备的生产排水宜采用直接接管排水,当设置事故地漏时,应采取气密措施。

6.1.5洁净区内的给排水管道应采用不易积存污物、易于清洗的材料,同时管道不宜设置在工艺设备上方。

6.1.6生产厂房内使用或接触酸碱类化学品的区域,应设置紧急淋浴洗眼器。

6.2工艺循环冷却水系统

6.2.1工艺循环冷却水系统应根据生产工艺要求的水温、水压条件进行设置。当水温、水压要求不同时宜分开设置。

6.2.2工艺循环冷却水系统的设置应符合下列规定:

1水泵宜采用变频调速控制;

2循环系统应设置备用泵,供水能力不应小于最大一台运行水泵的额定供水能力。

6.2.3工艺循环冷却水系统应设置过滤器及灭菌装置,过滤器宜备用,过滤精度应根据工艺设备对水质的要求确定。

6.2.4工艺循环冷却水系统的换热设备宜设置备用机组。

6.2.5循环水箱的有效容积不宜小于小时循环水量的10%,且应设置水位报警装置和自动及应急补水系统。

6.2.6工艺循环冷却水系统管道的设置应符合下列规定:

1管道应设置泄水阀、排气阀和排污口;

2工艺冷却水管道材质宜采用不锈钢管、给水UPVC管或聚丙烯PP管;

3管道附件与阀门材质宜与管道相同;

4采用不同金属材料的管道和支架时,管道和支架间的隔垫应采用绝缘材料。

6.2.7工艺循环冷却水系统应设置水质稳定处理装置。

6.3消防给水和灭火设备

6.3.1消防水泵及给水系统应符合现行国家标准《建筑设计防火规范》GB50016的有关规定。

6.3.2厂房应设置下列灭火系统:

1室内消火栓系统;

2自动喷水灭火系统;

3灭火器系统。

6.3.3生产厂房洁净生产层及洁净区吊顶或技术夹层内均宜设置湿式自动喷水灭火系统,设计参数宜符合表6.3.3的要求。

6.3.4洁净室内自动喷水灭火系统当采用干式自动喷水灭火系统或预作用自动喷水灭火系统时,管网容积及充水时间应符合现行国家标准《自动喷水灭火系统设计规范》GB50084有关规定,且系统计算作用面积应放大30%。

6.3.5在洁净区内各场所应配置灭火器,并应符合现行国家标准《建筑灭火器配置设计规范》GB50140的有关规定。

6.3.6洁净区内宜选用对工艺设备和洁净区环境不产生污染和腐蚀作用的灭火剂。

6.3.7洁净区内通道宜设置推车式二氧化碳灭火器。

7电气

7.1供配电

7.1.1供电电压应根据当地电网结构以及工厂负荷容量确定。

7.1.2用电负荷等级不宜低于二级,供电品质应满足封装测试工艺及设备要求,并应符合现行国家标准《供配电系统设计规范》GB50052的有关规定。

7.1.3低压配电电压等级应符合生产工艺设备及动力设备用电要求。

7.1.4工艺设备与动力设备的配电应分开设置。

7.1.5配电设备上方不宜设置水管。

7.2照明

7.2.1生产厂房内应设置供人员疏散用的应急照明,照度不应低于5.0lx。疏散标志应设置在安全出入口、疏散通道和疏散通道转角处。

7.2.2洁净区宜采用吸顶明装式灯具,当采用嵌入式灯具时,安装缝隙应采取密封措施。

7.2.3生产厂房备用照明设置应符合下列规定:

1洁净区内应设计备用照明;

2备用照明宜作为正常照明的一部分,且不宜低于该场所一般照明照度值的20%。

7.3接地

7.3.1生产设备的功能性接地、保护性接地、电磁兼容性接地、建筑防雷接地宜采用共用接地系统,接地电阻值应按其中最小值确定。

7.3.2生产设备的功能性接地与其他接地分开设置时,应设有防止雷电反击措施。分开设置的接地系统接地极宜与共用接地系统接地极保持20m以上的间距。

7.3.3生产厂房防雷接地设计应符合现行国家标准《建筑物防雷设计规范》GB50057的有关规定。

7.4防静电

7.4.1主要生产区应为一级防静电工作区。生产厂房防静电接地设计应符合现行国家标准《电子工程防静电设计规范》GB50611的有关规定。

7.4.2防静电工作区的地面应采用导静电型材料,导静电型地面电阻宜为2.5×104Ω~1×106Ω。

7.4.3生产厂房内导静电地面、工作台面、座椅等设施应作防静电接地。洁净室的墙面、门窗、吊顶的金属骨架应与接地系统可靠连接。

7.4.4防静电接地主干线截面不应小于95mm2,支线最小截面不应小于2.5mm2。

7.5通信与安全保护

7.5.1集成电路封装测试工厂内应设通信设施并应符合下列规定:

1厂房内电话(数据布线)应采用综合布线系统,综合布线系统的配线间或配线柜不应设置在工艺洁净区内;

2根据管理及工艺的需要应设置数据通信局域网及与因特网连接的接入网。

7.5.2生产厂房应设置火灾自动报警及消防联动控制系统。

7.5.3火灾自动报警系统应采用控制中心报警系统,防护对象的等级不应低于二级,并应符合下列规定:

1火灾自动报警系统应设有消防值班室,并应符合现行国家标准《建筑设计防火规范》GB50016的有关规定;

2控制设备的控制及显示功能应符合现行国家标准《火灾自动报警系统设计规范》GB50116的有关规定;

3生产厂房内火灾探测应采用智能型探测器。当在封闭房间内使用可燃气体及有机溶剂时,房间内应设置可燃气体探测器及火焰探测器;

4在洁净区空气处理设备的新风机出口及(或)循环风的回风口处宜设风管型火灾探测器。

7.5.4生产厂房内使用氮氢混合气体的区域应设置气体浓度监测报警装置。

7.5.5生产厂房应设置广播系统,洁净区内的扬声器宜采用洁净室型。当广播系统兼事故应急广播系统时应符合现行国家标准《火灾自动报警系统设计规范》GB50116的有关规定。

7.5.6工厂内宜设置闭路电视监控系统及门禁系统。

8净化空调及工艺排风

8.1净化空调

8.1.1净化空调系统的选型应根据洁净区面积、空气洁净度等级和产品生产工艺特点确定。

8.1.2气流流型的设计应满足生产工艺要求。当空气洁净度等级要求为6级~9级时,宜采用非单向流。当空气洁净度等级为5级时,应采用单向流或混合流。

8.1.3洁净区内的新鲜空气量应取下列两项中的最大值:

1补偿室内排风量和保持室内正压值所需新鲜空气量之和;

2保证供给洁净区内人员所需的新鲜空气量。

8.1.4洁净区与周围的空间应按照工艺要求保持正压,并应符合下列规定:

1不同等级的洁净区之间压差不宜小于5Pa;

2洁净区与非洁净区之间压差不应小于5Pa;

3洁净区与室外的压差不应小于5Pa。

8.1.5洁净区净化空调系统采用的方式应符合下列规定:

1净化空调系统宜设置集中新风处理系统,新风处理系统送风机应采取变频控制措施;

2净化空调循环系统应根据工艺生产流程、洁净度等级、温度、相对湿度、热负荷进行划分;

3循环空调系统宜采用干式冷却方式;

4采用室外空气与循环空气混合的空调系统时,宜设置二次回风。

8.1.6空气过滤器的选用和布置应符合下列规定:

1应根据空气洁净度等级选用空气过滤器类型和组合;

2空气过滤器的处理风量应小于或等于额定风量;

3空调机组的末级过滤器宜采用中效过滤器或亚高效过滤器,并应集中安装在空调箱的正压段;

4净化空调系统宜设置末端高效过滤器;

5同一净化空调系统内末端安装的高效过滤器的阻力、效率宜相近;

6同一净化空调系统内末端安装的高效过滤器的设计使用风量与额定风量的比值宜相近;

7安装在洁净厂房洁净区内的高效空气过滤器应采用不燃材料制作。

8.2冷热源

8.2.1工厂的冷热源设置应满足当地气候、能源结构、技术经济指标。

8.2.2在需要同时供冷和供热的工况下,冷水机组可根据负荷要求选用热回收机组,并宜采用自动控制方式调节机组的供热量。

8.2.3冷热源设备台数和单台容量应根据全年冷热负荷工况选择,并应保证设备在高、低负荷工况下均能安全、高效运行。冷热源设备宜设置不少于一台的备用机组。

8.2.4冬季或过渡季节室外温度较低的地区,可利用冷却塔作为冷源设备。

8.2.5冷水机组的冷冻水供、回水温差不应小于5℃,在满足工艺及空调用冷冻水温度时,应加大冷冻水供、回水温差和提高冷水机组的出水温度。

8.2.6冷冻水二次泵的单台容量选择应考虑全年负荷的最大值与最小值,同时冷冻水二次泵宜采用变频控制。

8.2.7锅炉房排放的大气污染物,应符合现行国家标准《锅炉大气污染物排放标准》GB13271的有关规定,以及当地大气污染物排放要求。

8.3工艺排风

8.3.1工艺排风系统设计应按照工艺设备排风性质设置独立的排风系统。

8.3.2工艺排风系统宜设置变频控制系统。

8.3.3工艺排风管道穿越防火墙或楼板处应设置防火阀。

8.3.4工艺排风管道应采用不燃材料,腐蚀性排风管道可采用难燃材料。

8.3.5排烟系统应符合现行国家标准《电子洁净厂房设计规范》GB50472的有关规定。

9纯水与废水处理

9.1纯水

9.1.1纯水系统设计应根据生产工艺要求,确定纯水制备系统规模、供水水质。当主体工程分期建设时,纯水系统应按最终规模统一规划、合理布局、分期实施。

9.1.2纯水制备、储存和输送设备和材料除应满足水量和水质要求外,并应光洁、平整,化学性质稳定。

9.1.3纯水系统应采用循环供水方式,并应符合下列规定:

1纯水输配系统的附加循环水量宜为额定耗用水量的20%~50%;

2纯水回水干管末端应设置背压调节阀组;

3纯水管道流速选择应能有效防止水质降低和微生物的滋生,并应兼顾压力损失。供、回水管流速不宜低于1.5m/s和0.5m/s;

4纯水输配管路不应出现死水滞留的管段;

5纯水输配管路系统应根据系统运行维护要求设置对应的采样口;

6工艺设备二次配管,隔离阀离设备较远时,宜安装回水管。

9.1.4纯水系统水质检测设备及仪表的检测范围和精度应符合纯水生产和检验的要求。

9.1.5纯水系统循环水泵宜采用变频控制,并宜设置备用泵。

9.1.6纯水系统抛光回路中所需的保持流量与水质的设备宜接入应急电源。

9.1.7纯水系统废水回收设计应与生产工艺设计密切配合,确定回收率。

9.2废水处理

9.2.1生产废水处理系统应根据废水污染物种类、水量、当地废水排放要求等设置分类收集、处理的废水处理系统。

9.2.2腐蚀性废水有压管道在穿越人员密集区域时应采用双层管道,不宜采用法兰连接。

9.2.3生产废水处理系统易发生故障及需定期维修的部件应按不少于一台备用配置。输送系统及提升用水泵宜采用应急电源供电。

9.2.4生产废水处理系统应设置应急废水收集池。应急废水收集池的容积不宜小于8h排放量并应满足项目环境影响评价报告的要求。

9.2.5生产废水系统应设置调节池,连续处理系统的调节池容积不宜小于4h排放量,间歇处理系统的调节池容积不应小于一个处理周期的排放量。

9.2.6废水处理系统设备及构筑物应设置排空设施,并应根据废水水质采取防腐措施。

9.2.7废水处理系统化学品储罐周围应设置围堰。

10气体与真空

10.1大宗气体

10.1.1大宗气体供应系统宜采用在厂区内设置制气装置或外购液态气储罐和瓶装气体方式。

10.1.2大宗气体供应系统宜设置气体质量监控系统。

10.1.3当气体的纯度大于99.9999%、露点低于—40℃时,大宗气体应设置终端气体纯化装置,气体终端纯化装置应设置在用气点处。

10.1.4生产厂房内的大宗气体管道等应采取下列技术措施:

1管道及阀门附件内壁处理等级应满足输送气体的品质要求;

2混合气体管道的终端或最高点应设置放散管,放散管口应设置阻火器;

3混合气体管道应设置导出静电的设施;

4混合气体引入管道上应设置自动切断阀。

10.1.5气体管道和阀门应根据产品生产工艺要求选择,宜符合下列规定:

1当气体纯度大于99.99%、露点低于—40℃时,宜采用内壁处理的不锈钢管,阀门宜采用波纹管阀或球阀;

2气体管道阀门、附件的材质宜与相连接的管道材质一致。

10.1.6气体管道连接,宜符合下列规定:

1管道连接宜采用焊接,不锈钢管宜采用氩弧焊;

2管道与设备或阀门的连接,宜采用表面密封接头,密封材料宜采用金属垫或聚四氟乙烯垫。

10.2干燥压缩空气

10.2.1干燥压缩空气系统应根据产品生产工艺要求、供气量和供气品质等因素确定,并应符合下列规定:

1供气规模应按生产工艺平均用气量及系统损耗量确定;

2供气设备可集中布置在生产厂房内的供气站或生产厂房外的综合动力站;

3供气品质应根据生产工艺对含水量、含油量、微粒粒径的要求确定。

10.2.2空气压缩机及冷冻式干燥装置的布置应保证冷却空气排放至室外,防止热空气混入冷却空气的入口。

10.2.3水冷式空压机组宜采用闭式循环水系统。

10.2.4干燥压缩空气管道内输送露点低于—40℃时,可采用不锈钢管或镀锌钢管,阀门宜采用球阀。

10.2.5压缩空气系统管道设计应符合下列规定:

1压缩空气主管道直径应按全系统平均用气量确定,主支管道直径应按局部系统平均用气量确定,支管道直径应按设备最大用气量确定;

2干燥压缩空气输送露点低于—40℃时,用于管道连接的密封材料宜选用金属垫片或聚四氟乙烯垫片;

3管道连接宜采用焊接,不锈钢管应采用氩弧焊。

10.3真空

10.3.1生产厂房工艺真空系统设计应符合下列规定:

1工艺真空系统的抽气能力应按生产工艺实际用气量及系统损耗量确定;

2供气设备应布置在生产厂房内的一个或多个供气站内;

3工艺真空系统宜设置真空压力过低保护装置。

10.3.2工艺真空系统管道设计应符合下列规定:

1工艺真空管路应采用树枝状布置形式。

2工艺真空主管道直径应按照系统实际抽气量确定;主支管道直径应按局部系统实际抽气量确定;支管道直径应按设备最大抽气量确定。

3工艺真空系统管道材料宜根据工艺真空系统的真空压力及真空特性选用。真空站房内应采用镀锌钢管,站房外的室内真空管道宜采用镀锌钢管或厚壁聚氯乙烯管道。

附录A集成电路封装测试厂工艺流程

A.0.1通孔插装型封装宜采用下列生产工艺流程:

A.0.2球栅阵列封装宜采用下列生产工艺流程:

A.0.3晶圆级封装宜采用下列生产工艺流程:

本规范用词说明

1为便于在执行本规范条文时区别对待,对要求严格程度不同的用词说明如下:

1)表示很严格,非这样做不可的:

正面词采用“必须”,反面词采用“严禁”;

2)表示严格,在正常情况下均应这样做的:

正面词采用“应”,反面词采用“不应”或“不得”;

3)表示允许稍有选择,在条件许可时首先应这样做的:

正面词采用“宜”,反面词采用“不宜”;

4)表示有选择,在一定条件下可以这样做的,采用“可”。

2条文中指明应按其他有关标准执行的写法为:“应符合……的规定”或“应按……执行”。

引用标准名录

《锅炉大气污染物排放标准》GB13271

《建筑设计防火规范》GB50016

《采暖通风与空气调节设计规范》GB50019

《供配电系统设计规范》GB50052

《洁净厂房设计规范》GB50073

《火灾自动报警系统设计规范》GB50116

《建筑内部装修设计防火规范》GB50222

《电子工业洁净厂房设计规范》GB50472

《电子工程防静电设计规范》GB50611

《建筑物防雷设计规范》GB50057

《自动喷水灭火系统设计规范》GB50084

中华人民共和国国家标准

集成电路封装测试厂设计规范

GB51122-2015

条文说明

制订说明

《集成电路封装测试厂设计规范》GB51122-2015,经住房城乡建设部2015年8月27日以第887号公告批准发布。

本规范制订过程中,编制组进行了广泛的调查研究,紧密结合当前我国电子信息产品制造业对集成电路封装测试的需求,切实体现了我国集成电路封装测试工厂工程建设中新技术、新工艺、新设备和新材料的应用成果和先进经验;特别是参考和借鉴了国内已建成的数十条集成电路封装测试生产线工程的先进技术和运行经验,做到了既结合国情又与国际同类标准接轨。开展了必要的技术研讨,并广泛征求有关单位的意见,最后经有关部门共同审查定稿。

为便于广大设计、施工、科研、学校等单位有关人员在使用本规范时能正确理解和执行条文规定,本规范编制组按章、节、条顺序编制了本规范的条文说明,对条文规定的目的、依据及执行中需注意的有关事项进行了说明,还着重对强制性条文的强制性理由作了解释。但是,本条文说明不具备与规范正文同等的法律效力,仅供使用者作为理解和把握规范规定的参考。

22年初心不变,只为做好一件事,合景智慧建设(广东)有限公司始终认为,一个好的产品,必须是优质的洁净空间所赋予的品质。合景净化,行业知名品牌净化工程公司,您值得托付。

22年初心不变,只为做好一件事,合景智慧建设(广东)有限公司始终认为,一个好的产品,必须是优质的洁净空间所赋予的品质。合景净化,行业知名品牌净化工程公司,您值得托付。 22年初心不变,只为做好一件事,合景智慧建设(广东)有限公司始终认为,一个好的产品,必须是优质的洁净空间所赋予的品质。合景净化,行业知名品牌净化工程公司,您值得托付。

22年初心不变,只为做好一件事,合景智慧建设(广东)有限公司始终认为,一个好的产品,必须是优质的洁净空间所赋予的品质。合景净化,行业知名品牌净化工程公司,您值得托付。 22年初心不变,只为做好一件事,合景智慧建设(广东)有限公司始终认为,一个好的产品,必须是优质的洁净空间所赋予的品质。合景净化,行业知名品牌净化工程公司,您值得托付。

22年初心不变,只为做好一件事,合景智慧建设(广东)有限公司始终认为,一个好的产品,必须是优质的洁净空间所赋予的品质。合景净化,行业知名品牌净化工程公司,您值得托付。 22年初心不变,只为做好一件事,合景智慧建设(广东)有限公司始终认为,一个好的产品,必须是优质的洁净空间所赋予的品质。合景净化,行业知名品牌净化工程公司,您值得托付。

22年初心不变,只为做好一件事,合景智慧建设(广东)有限公司始终认为,一个好的产品,必须是优质的洁净空间所赋予的品质。合景净化,行业知名品牌净化工程公司,您值得托付。 22年初心不变,只为做好一件事,合景智慧建设(广东)有限公司始终认为,一个好的产品,必须是优质的洁净空间所赋予的品质。合景净化,行业知名品牌净化工程公司,您值得托付。

22年初心不变,只为做好一件事,合景智慧建设(广东)有限公司始终认为,一个好的产品,必须是优质的洁净空间所赋予的品质。合景净化,行业知名品牌净化工程公司,您值得托付。

![[完工案例]飞鹤乳业厂房净化工程建设总包项目完工视频111](https://www.hejiejh.com/article_file/1690191387693_c.png)

![[施工现场]半导体芯片十级百级无尘车间施工视频111](https://www.hejiejh.com/article_file/1750054391705.jpg)

![[完工案例]鹏辉能源洁净厂房建设总包项目完工视频111](https://www.hejiejh.com/article_file/1692436812963_c.png)

![[马来西亚工程项目]医疗器械GMP总包项目案例111](https://www.hejiejh.com/article_file/1754292803847_c.png)